## IMPLEMENTATION ATTACKS: FROM THEORY TO PRACTICE

### **DISSERTATION**

zur Erlangung des Grades eines Doktor-Ingenieurs der Fakultät für Elektrotechnik und Informationstechnik an der Ruhr-Universität Bochum

> by David Oswald Bochum, September 2013

Copyright © 2013 by David Oswald. All rights reserved. Printed in Germany.

David Oswald Place of birth: Essen, Germany Author's contact information: david.oswald@rub.de www.kasper-oswald.de

Thesis Advisor: Prof. Dr.-Ing. Christof Paar

Ruhr-Universität Bochum, Germany

Secondary Referee: Prof. David Naccache

Université Paris II / ENS, France

Thesis submitted: June 18, 2013 Thesis defense: August 1, 2013. Last revision: September 16, 2013.

Du bist wie eine Blume, So hold und schön und rein; Ich schau dich an, und Wehmut Schleicht mir ins Herz hinein.

Mir ist, als ob ich die Hände Aufs Haupt dir legen sollt, Betend, daß Gott dich erhalte So rein und schön und hold

Heinrich Heine.

## **Abstract**

Embedded devices have become omnipresent both in business applications and in the private sector. Various, highly diverse types of systems rely on embedded computing devices that, compared to traditional PCs, are often not directly noticed by the user. Examples for such embedded devices are manifold: RFID-based smartcards are on the way to replacing magnetic-stripe cards for payments and are wide-spread in public transport and user identification. Long-range RFID transponders are used for identifying and managing large assets like freight containers in the supply chain. A modern car comprises a large number of microcontrollers, controlling numerous components ranging from the engine to the immobilizer. Consumer products like mobile phone batteries and inkjet cartridges are equipped with special-purpose chips to prevent counterfeit. Access to online services is secured with hardware tokens for two-factor authentication, and electronic door locks for controlling the physical access to buildings and offices are on their way to replacing traditional mechanical systems.

With the increasing reliance on embedded devices arises the need to thoroughly examine the related security mechanisms. Malicious adversaries can cause severe financial losses, e.g., due to IP counterfeit, industrial espionage, or fraudulent payment transactions, but also endanger material and even human lives, e.g., in the case of vehicles, medical devices, or industrial machinery. Hence, many embedded devices incorporate protection mechanisms, often involving cryptographic functionality to fulfill requirements like confidentiality, authenticity, and integrity. To evaluate the security level of according implementations, a purely mathematical point of view is not sufficient:

Classical cryptanalysis considers an algorithm as an ideal construct for which only the inputs and outputs are known to an adversary, however, for real-world devices, this assumption does not hold. The actual hardware or software realization of a cryptographic primitive is subject to implementation attacks that utilize physical properties to break analytically secure schemes like AES, 3DES, or RSA. Active fault injection techniques allow to extract secret information by disturbing the cryptographic computation, e.g., exposing the device to over and undervoltages or UV-C and laser light. In contrast, passive side-channel analysis is based on monitoring the behavior of the target device while executing a cryptographic algorithm, e.g., by measuring the power consumption or the EM emanation.

Interestingly, the practical threat posed by implementation attacks and particularly sidechannel analysis to embedded devices has received relatively little attention in the scientific community. This is in contrast to the in-depth treatment of the theory of such attacks in the scientific community. The goal of this thesis is to fill this gap and evaluate the physical security of widely used devices, with a special focus on side-channel analysis. We propose improved digital and analog pre-processing techniques to increase the quality of side-channel measurements and describe tools to perform implementation attacks at a low cost. Amongst others, we present circuits to isolate the leakage of contactless smartcards and introduce the GIAnT, a cost-efficient FPGA-based platform for controlling target devices and conducting side-channel and fault injection attacks.

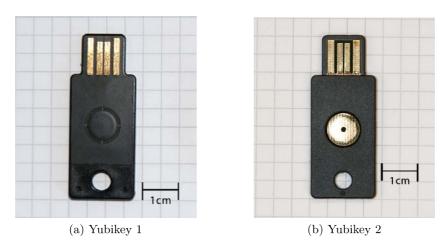

Applying the developed tools, the cryptographic functionality of several products representing different classes of embedded devices is analyzed. The examples include RFID transponders used in the supply chain, a contactless smartcard (the Mifare DESFire MF3ICD40), an electronic locking system by SimonsVoss, a two-factor authentication token (the Yubikey 2), SHA-1-based anti-counterfeiting chips by Maxim Integrated, and Altera Stratix II FPGAs. In all cases, we show that implementation attacks and side-channel analysis in particular can circumvent the (cryptographic) protection of the examined devices. Since the demonstrated attacks can be put into practice with a relatively low financial effort, it appears to be mandatory to include suitable countermeasures in new product generations. In this regard, we discuss possible approaches, taking the often limited resources available in embedded applications into account. As a concluding result, we outline directions for further research, both from an adversary's point of view and from a constructive perspective.

#### Keywords.

Cryptography, implementation attacks, side-channel analysis, real-world attacks, contact-less smartcards, Mifare DESFire MF3ICD40, RFID, electronic locks, SimonsVoss, two-factor authentication, Yubikey, anti-counterfeit, Altera Stratix II, bitstream encryption, reverse-engineering, IP protection, countermeasures

## Kurzfassung

#### Implementierungsangriffe: Von der Theorie zur Praxis

Eingebettete Systeme sind heute sowohl im geschäftlichen Bereich als auch in Produkten für Endkunden allgegenwärtig. Eine Vielzahl stark unterschiedlicher Anwendungen basiert auf eingebetteten Prozessoren, die verglichen mit traditionellen PCs für den Anwender oft unsichtbar sind. Die Beispiele in dieser Hinsicht sind zahlreich: Kontaktlose Smartcards ersetzen klassische Karten mit Magnetstreifen in Bezahlsystemen und sind schon heute weit verbreitet im öffentlichen Nahverkehr und für Identitätsdokumente. RFID-Transponder mit hohen Reichweiten werden zur Identifikation von z.B. Frachtcontainern in der Logistik eingesetzt. Ein modernes Auto beinhaltet viele Mikrocontroller, die Steuerungsaufgaben vom Motor bis hin zur Wegfahrsperre übernehmen. Massenprodukte wie Mobiltelefon-Akkus oder Druckerpatronen werden mit speziellen Chips versehen, um Produktpiraterie entgegenzuwirken. Der Zugang zu Online-Anwendungen wird mit Zwei-Faktor-Authentifizierung auf Basis von Hardware-Tokens gesichert und elektronische Schließsysteme ersetzen mechanische Lösungen.

Im Zuge der stetig wachsenden Verbreitung eingebetteter Systeme stellt sich die Frage nach der Sicherheit in entsprechenden Anwendungen. Böswillige Angreifer können neben finanziellen Verlusten—z.B. durch Fälschung von Produkten, Industriespionage oder betrügerische Zahlungs-Transaktionen—auch unmittelbar Sachschäden herbeiführen und im schlimmsten Fall Menschenleben gefährden, z.B. bei Automobilen, medizinischen Geräten oder Industrieanlagen. Daher verfügen zahlreiche eingebettete Geräte über entsprechende Schutzmaßnahmen. Oft wird Kryptographie verwendet, um Sicherheitsziele wie Vertraulichkeit, Authentizität und Integrität zu realisieren. Um das tatsächliche Sicherheitsniveau entsprechender Implementierungen zu bewerten, ist im Kontext eingebetteter Systeme eine rein mathematische Untersuchung nicht hinreichend:

Die klassische Kryptanalyse betrachtet einen kryptographischen Algorithmus als ein idealisiertes Konstrukt, bei dem für einen Angreifer nur die Ein- und Ausgabewerte bekannt sind. Für praktische Umsetzungen ist diese Annahme jedoch ungültig. Implementierungsangriffe zielen unmittelbar auf die Hard- und Software eines Gerätes und verwenden physikalische Eigenschaften, um mathematisch sichere Verfahren wie AES, 3DES oder RSA zu brechen. So kann z.B. mittels aktiver Fehlerinjektion die Ausführung eines Algorithmus gestört und geheime Daten extrahiert werden. Im Gegensatz dazu basieren Seitenkanal-Analysen auf der passiven Messung physikalischer Größen, z.B. der Stromaufnahme oder der EM-Abstrahlung einer Schaltung.

Die praktische Bedrohung durch Implementierungsangriffe und insbesondere durch Seitenkanal-Analyse wurde bislang in geringem Maße wissenschaftlich untersucht. Das Ziel dieser Dissertation ist es daher, in dieser Hinsicht weitere Untersuchungen an weitverbreiteten eingebetteten Systemen mit einem speziellen Fokus auf Seitenkanal-Analysen durchzuführen. Zu diesem Zweck werden zunächst analoge wie digitale Vorverarbeitungsmethoden betrachtet, die die Qualität entsprechender Messdaten erhöhen können. Darüber hinaus werden Werkzeuge vorge-

stellt, mit denen Implementierungsangriffe kostengünstig umgesetzt werden können. Dies beinhaltet u.a. Schaltungen zur Rückgewinnung des Seitenkanal-Signals kontaktloser Smartcards und GIAnT, eine FPGA-Plattform zur Steuerung der analysierten Geräte und zur Realisierung von Seitenkanal- und Fehlerinjektions-Angriffen.

Mit den entwickelten Werkzeugen wird im Anschluss die Sicherheit spezifischer Produkte—die repräsentativ für verschiedene Arten von eingebetteten System sind—geprüft. Im Rahmen der durchgeführten Fallstudien werden RFID-Transponder für Supply Chain Anwendungen, eine kontaktlose Smartcard (Mifare DESFire MF3ICD40), ein elektronisches Schließssystem von SimonsVoss, ein Zwei-Faktor Authentifizierungstoken (Yubikey 2), SHA-1-basierte Chips zum Fälschungsschutz von Maxim Integrated und Altera Stratix II FPGAs untersucht. In allen Fällen zeigte sich, dass mit Implementierungsangriffen und insbesondere Seitenkanal-Analysen die (kryptographischen) Schutzmaßnahmen erfolgreich umgangen werden können. Da die vorgestellten Angriffe mit relativ kostengünstiger technischer Ausrüstung umgesetzt wurden, erscheint es unumgänglich, bei der Entwicklung neuer Produkte entsprechende Gegenmaßnahmen zu berücksichtigen. Mögliche Ansätze in dieser Hinsicht werden unter Berücksichtigung der oft begrenzten Ressourcen in eingebetteten Anwendungen betrachtet. Abschließend werden relevante Forschungsthemen im Bereich der eingebetteten Sicherheit—sowohl aus der Sicht eines Angreifers als auch eines Entwicklers—identifiziert und näher beschrieben.

#### Schlagworte.

Kryptographie, Implementierungsangriffe, Seitenkanal-Analyse, Praktische Angriffe, Kontaktlose Smartcards, Mifare DESFire MF3ICD40, RFID, Elektronische Schließsysteme, Simons-Voss, Zwei-Faktor Authentifizierung, Yubikey, Schutz vor Produktfälschungen, Altera Stratix II, Bitstrom-Verschlüsselung, Reverse-Engineering, Gegenmaßnahmen

## **Acknowledgements**

It has been about four years since I began working on my PhD at the Chair for Embedded Security, and now finally I managed to write all the stuff down. So it is only fitting—before starting with the dull science—to say thanks to the people that enabled me to go my way.

First of all, I want to send all my love to the wonderful Jelena Ninić who shines like an always bright sun in my live—and who drew the fantastic below picture before my defense to help me relax. Sunce, thanks for all your support and love, volim te!

Lots of thanks go to my parents Hetti and Detlef for giving me the opportunity to study in the first place and teaching me many important things about life and science. Thanks also to the rest of my vast family and all my friends, you are great, guys!

Coming to the professional part, first, I'd like to thank my advisor Christof Paar who has been an excellent teacher (and not only for scientific matters) in the past years. With his broad perspective and open-mindedness, Christof has a unique way of giving interesting topics to the right people. 1000 Dank! Thanks go also to David Naccache for co-advising my thesis and managing to combine this job with his numerous other duties and responsibilities—merci!

Next in line are all the people who I got to know during my time at Emsec. First, thanks go to Timo Kasper, with whom I share a (chaotic) office (and phone) for many years now, wrote many papers and went to many conferences with, and with whom I finally managed to set up a company. Danke, Dr. Kasper. Besides, I am obliged to the non-scientific staff at Emsec, that is, Irmgard (our team assistant) and Horst (our admin). Thanks for keeping the group up and running. Of course, I also did not forget my various co-authors, so here is the list (in alphabetical order): Roberto Avanzi, Benedikt Driessen, Tim Güneysu, Ilya Kizhvatov, Alexander Kühn, Gregor Leander, Nilesh Madhu, Ingo von Maurich, Amir Moradi, Bastian Richter, Falk Schellenberg, Jörn-Marc Schmidt, Daehyun Strobel, Pawel Swierczynski, Michael Tunstall, and Christian Zenger. Thanks, guys!

Finally, when thinking about whom to thank, some other people I owe gratitude to came to my mind: The students who I supervised and who helped me to advance with my PhD, the guys at CRI (where I was intern for a few months), Thomas Eisenbarth (and Ricarda and Finn and David) for their hospitality, the people at my sports club (Essener Hap Ki Do Sportclub e.V.), and a few university teachers who I particularly remember: Roberto Avanzi, Helmut Jacob, and Günter Felbecker. I hope I did not forget anyone, but if I did and I owe you thanks, you probably know. Having said that, let us come to the science, then—and to motivate what follows with the words of Carl Sagan: "We live in a society exquisitely dependent on science and technology, in which hardly anyone knows anything about science and technology."

Thanks!

## **Table of Contents**

|   | Imprint Preface Abstract Kurzfassung Acknowledgements |         |                                                                           |    |  |  |  |

|---|-------------------------------------------------------|---------|---------------------------------------------------------------------------|----|--|--|--|

| I | Pr                                                    | elimina | aries                                                                     | 1  |  |  |  |

| 1 | Intr                                                  | oductio | on                                                                        | 3  |  |  |  |

|   | 1.1                                                   | Motiva  | ation                                                                     | 3  |  |  |  |

|   | 1.2                                                   | Impler  | mentation Attacks                                                         | 6  |  |  |  |

|   | 1.3                                                   | Struct  | ture of this Thesis                                                       | 8  |  |  |  |

|   | 1.4                                                   | Summ    | nary of Research Contributions                                            | 9  |  |  |  |

|   |                                                       | 1.4.1   | SCA Pre-Processing                                                        | 9  |  |  |  |

|   |                                                       | 1.4.2   | Tools                                                                     | 9  |  |  |  |

|   |                                                       | 1.4.3   | Practical Implementation Attacks                                          | 10 |  |  |  |

| 2 | Side                                                  | -Chann  | nel Analysis                                                              | 13 |  |  |  |

|   | 2.1                                                   |         | luction                                                                   | 13 |  |  |  |

|   | 2.2                                                   | Physic  | cal Side Channels                                                         | 14 |  |  |  |

|   |                                                       | 2.2.1   | Execution Time                                                            | 14 |  |  |  |

|   |                                                       | 2.2.2   | Power Consumption                                                         | 15 |  |  |  |

|   |                                                       | 2.2.3   | Electro-Magnetic Emanation                                                |    |  |  |  |

|   |                                                       | 2.2.4   | Other Side Channels                                                       |    |  |  |  |

|   | 2.3                                                   | Evalua  | ation Methods                                                             | 20 |  |  |  |

|   |                                                       | 2.3.1   | Simple Power Analysis                                                     | 21 |  |  |  |

|   |                                                       | 2.3.2   | Differential Techniques using Statistics: Differential Power Analysis and |    |  |  |  |

|   |                                                       |         | Correlation Power Analysis                                                | 21 |  |  |  |

|   |                                                       | 2.3.3   | Template Attacks                                                          | 24 |  |  |  |

|   |                                                       | 2.3.4   | Other Methods                                                             | 26 |  |  |  |

|   | 2.4                                                   | Pre-Pr  | rocessing Methods                                                         | 26 |  |  |  |

|   |                                                       | 2.4.1   | Linear Filters                                                            | 27 |  |  |  |

|   |                                                       | 2.4.2   | SCA in the Frequency Domain                                               | 27 |  |  |  |

|   | 2.5                                                   | Findin  | ng Optimal Linear Transforms for SCA                                      | 28 |  |  |  |

|   |                                                       | 2.5.1   | Contribution                                                              | 28 |  |  |  |

|   |                                                       | 2.5.2   | Matrix Notation                                                           |    |  |  |  |

|   |                                                       | 2.5.3   | Optimal Linear Transforms for CPA                                         | 30 |  |  |  |

#### Table of Contents

|    | 2.6  | 2.5.4 Simulation Results                        | 31<br>35<br>38 |

|----|------|-------------------------------------------------|----------------|

| II | То   | ools                                            | 39             |

| 3  | Mea  | asurement and Evaluation                        | 41             |

|    | 3.1  | Receiving and Transmitting RF Signals           | 41             |

|    |      | 3.1.1 The USRP2                                 | 41             |

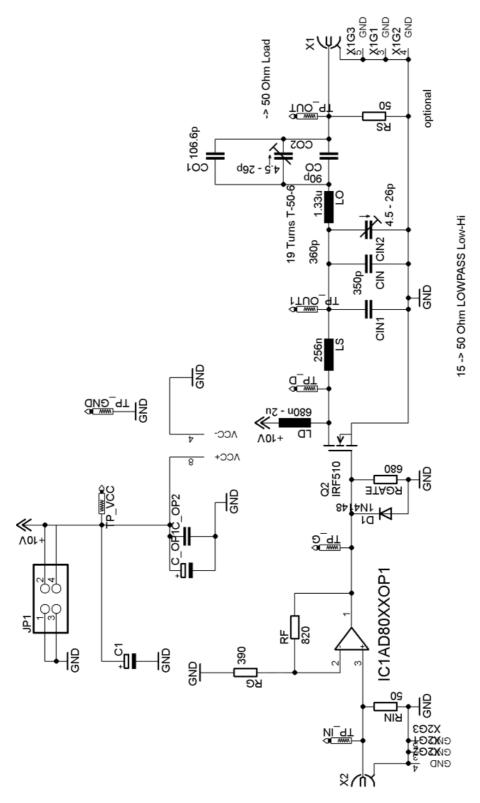

|    |      | 3.1.2 Custom RFID Reader                        | 43             |

|    | 3.2  | Side-Channel Measurement                        | 44             |

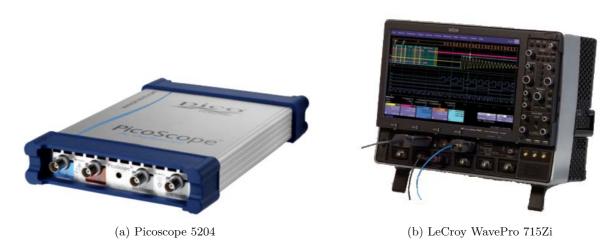

|    |      | 3.2.1 Oscilloscopes                             | 44             |

|    |      | 3.2.2 Amplifiers and EM Probes                  | 45             |

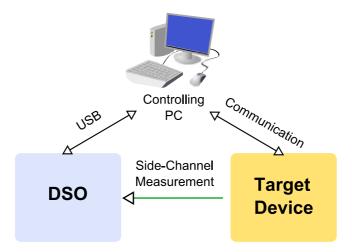

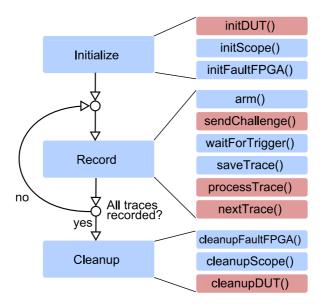

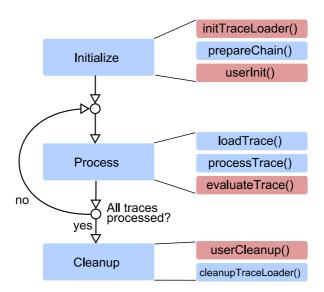

|    |      | 3.2.3 Measurement Framework                     | 46             |

|    | 3.3  | Evaluation Framework                            | 48             |

|    | 3.4  | Conclusion                                      | 49             |

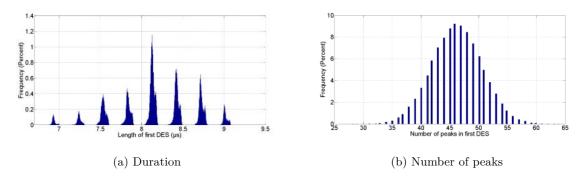

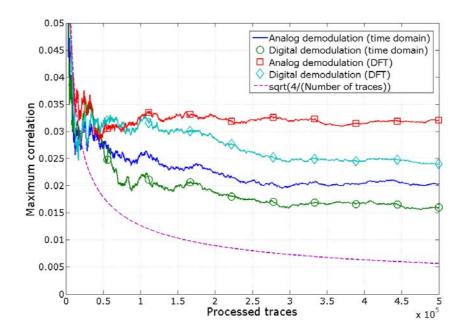

| 4  | Pre- | -Processing for SCA of RFID                     | 51             |

| •  | 4.1  | Introduction                                    | 51             |

|    |      | 4.1.1 Contribution                              | 52             |

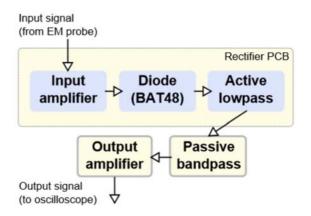

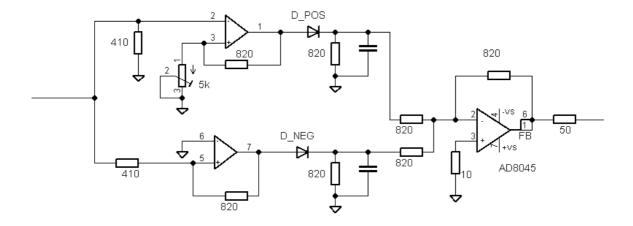

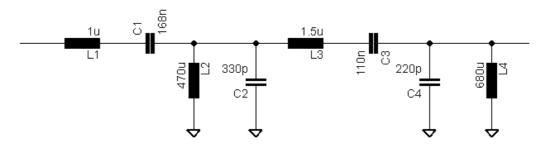

|    | 4.2  | Half-Wave Rectifier                             | 52             |

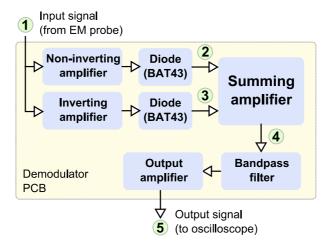

|    | 4.3  | Full-Wave Rectifier                             | 53             |

|    | 4.4  | Digital Processing                              | 54             |

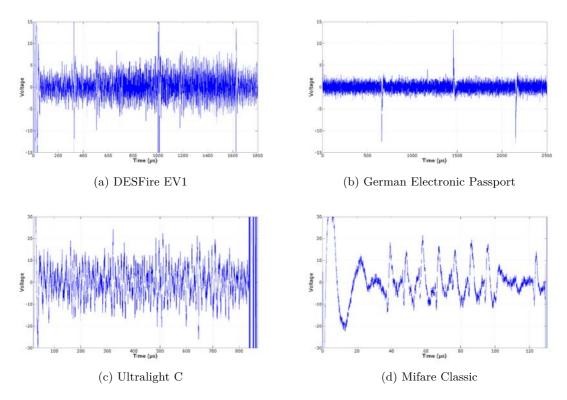

|    | 4.5  | Measurements for Various Contactless Smartcards | 55             |

|    | 4.6  | Conclusion                                      | 57             |

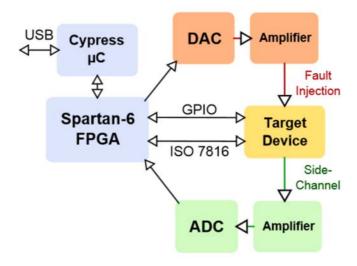

| 5  | GΙΔ  | nT: A Platform for Implementation Attacks       | 59             |

| Ŭ  | 5.1  | Introduction                                    | 59             |

|    | 5.2  | System Overview                                 | 59             |

|    |      | 5.2.1 Analog Input and Output                   | 60             |

|    |      | 5.2.2 Communication Interfaces                  | 62             |

|    |      | 5.2.3 Programming and Control Interface         | 63             |

|    | 5.3  | Practical Verification                          | 65             |

|    |      | 5.3.1 Target Device 1: ATXMega256               | 65             |

|    |      | 5.3.2 Target Device 2: ATMega163 Smartcard      | 69             |

|    | 5.4  | Conclusion                                      | 70             |

|    |      |                                                 |                |

|    | Re   | eal-World Attacks                               | 71             |

| 6  | DEI  | D. Pango Maasuroments                           | 73             |

| U  | 6.1  | D Range Measurements Introduction               | 73             |

|    | 0.1  | 6.1.1. Related Work                             | 74<br>74       |

|   |      | 6.1.2 Contribution                                                        | 74 |

|---|------|---------------------------------------------------------------------------|----|

|   | 6.2  |                                                                           | 75 |

|   | 6.3  | ·                                                                         | 76 |

|   |      |                                                                           | 76 |

|   |      |                                                                           | 77 |

|   |      |                                                                           | 80 |

|   |      | 1                                                                         | 82 |

|   | 6.4  |                                                                           | 85 |

|   | 0.1  |                                                                           | 85 |

|   |      |                                                                           | 85 |

|   |      | 9                                                                         | 86 |

|   |      | 1                                                                         | 87 |

|   | 6.5  |                                                                           | 90 |

|   | 0.0  |                                                                           | 90 |

|   |      | *                                                                         | 91 |

|   |      | 0.5.2 Implications for Official Territoria.                               | 91 |

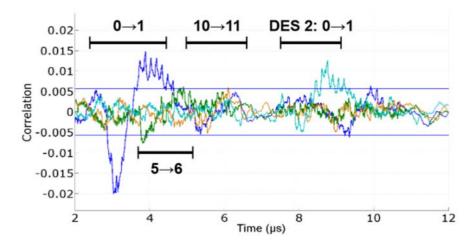

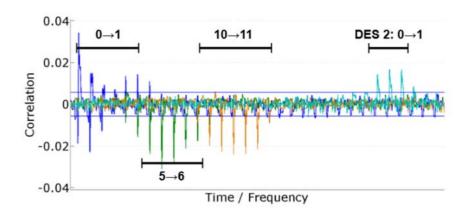

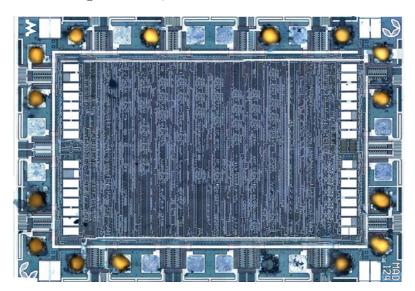

| 7 | Mifa | are DESFire MF3ICD40                                                      | 93 |

|   | 7.1  | Introduction                                                              | 93 |

|   |      |                                                                           | 94 |

|   |      |                                                                           | 94 |

|   | 7.2  |                                                                           | 95 |

|   | 7.3  |                                                                           | 96 |

|   |      | 9                                                                         | 98 |

|   |      | 7.3.2 Full Key-Recovery                                                   |    |

|   | 7.4  | Template Attack on the Key Transfer                                       |    |

|   | 7.5  | Analysis of a Real-World System: The Opencard                             |    |

|   | 7.6  | Conclusion                                                                |    |

|   | •••  |                                                                           |    |

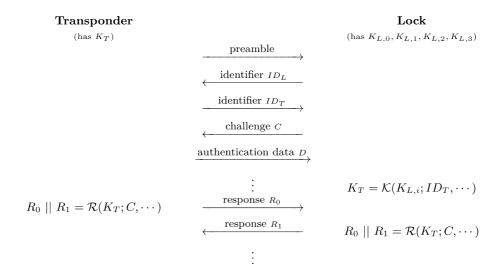

| 8 | Simo | onsVoss Access Control System 10                                          | 09 |

|   | 8.1  | Introduction                                                              | 09 |

|   |      | 8.1.1 Related Work                                                        | 10 |

|   |      | 8.1.2 Contribution                                                        | 11 |

|   | 8.2  | Reverse-Engineering a Black-Box System                                    | 11 |

|   |      | 8.2.1 Radio Protocol                                                      |    |

|   |      | 8.2.2 Hardware and Circuit Boards                                         | 11 |

|   |      | 8.2.3 Extracting and Reverse-Engineering the Firmware of the PIC 1        | 13 |

|   | 8.3  | SimonsVoss's Proprietary Cryptography                                     |    |

|   | 8.4  | Extraction of the System Key with SCA                                     |    |

|   |      | 8.4.1 Theoretical Attack: Predicting Intermediate Values of the Obscurity |    |

|   |      | Function in the Key Derivation                                            | 16 |

|   |      | 8.4.2 Practical Results                                                   |    |

|   | 8.5  | Conclusion                                                                |    |

|   | 0.0  |                                                                           | 10 |

| 9 | The  | Yubikey One-Time Password Token 12                                        | 21 |

|   | 9.1  | •                                                                         | 21 |

|   |      | 9.1.1 Two-Factor Authentication                                           | 22 |

#### Table of Contents

|    |      | 9.1.2 Adversary Model                                         |

|----|------|---------------------------------------------------------------|

|    |      | 9.1.3 Related Work                                            |

|    |      | 9.1.4 Contribution                                            |

|    | 9.2  | The Yubikey 2                                                 |

|    |      | 9.2.1 Typical Use                                             |

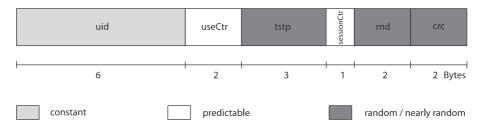

|    |      | 9.2.2 OTP Structure                                           |

|    |      | 9.2.3 Hardware of the Yubikey 2                               |

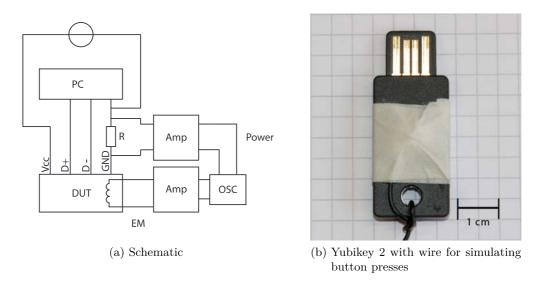

|    | 9.3  | Measurement Setup                                             |

|    | 9.4  | Side-Channel Profiling                                        |

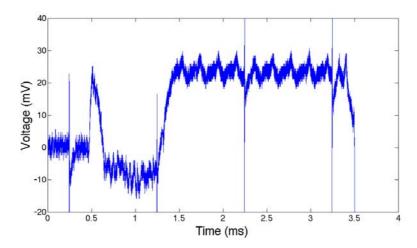

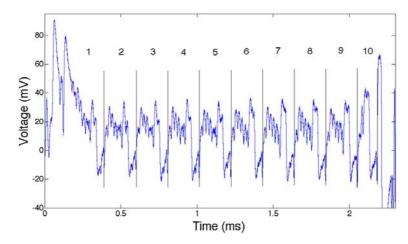

|    |      | 9.4.1 Locating the AES Encryption                             |

|    |      | 9.4.2 EM Measurements                                         |

|    | 9.5  | Extracting the AES Key                                        |

|    |      | 9.5.1 Key Recovery using Power Traces                         |

|    |      | 9.5.2 Key Recovery using EM Traces                            |

|    | 9.6  | Conclusion                                                    |

|    | 9.7  | Reaction of the Vendor                                        |

|    |      |                                                               |

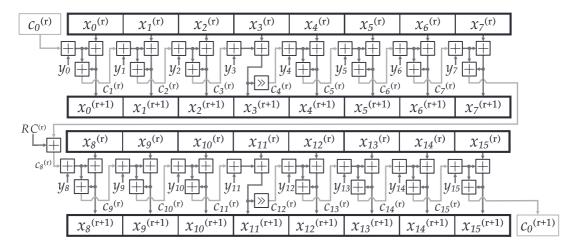

| 10 | Max  | im SHA-1 Product Authentication ICs 13                        |

|    | 10.1 | Introduction                                                  |

|    |      | 10.1.1 Related Work                                           |

|    |      | 10.1.2 Contribution                                           |

|    | 10.2 | Authentication Protocol                                       |

|    |      | Theoretical Attack                                            |

|    |      | Side-Channel Profiling                                        |

|    |      | Side-Channel Key Extraction                                   |

|    |      | Initial Results for FI                                        |

|    |      | Conclusion                                                    |

|    |      |                                                               |

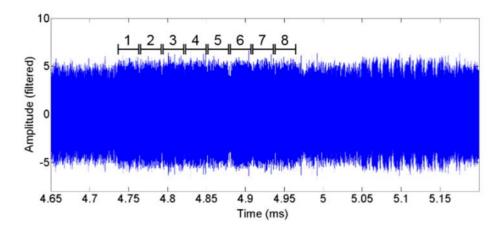

| 11 | Alte | ra FPGA Bitstream Encryption 14                               |

|    | 11.1 | Introduction                                                  |

|    |      | 11.1.1 Related Work                                           |

|    |      | 11.1.2 Contribution                                           |

|    | 11.2 | Reverse-Engineering the Design Security Scheme                |

|    |      | 11.2.1 Preliminaries                                          |

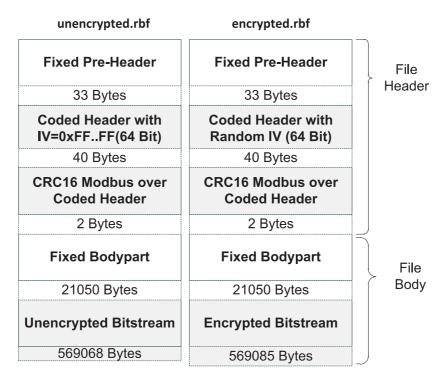

|    |      | 11.2.2 RBF File Format                                        |

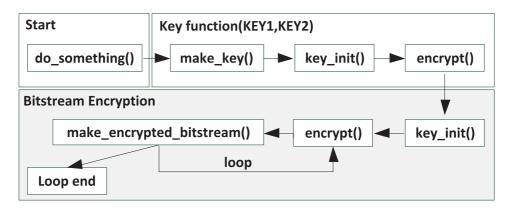

|    |      | 11.2.3 AES Key Derivation                                     |

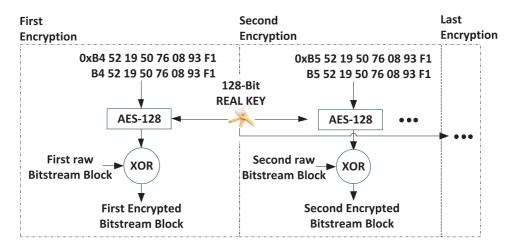

|    |      | 11.2.4 AES Encryption Mode                                    |

|    | 11.3 | Side-Channel Profiling                                        |

|    |      | 11.3.1 Measurement Setup                                      |

|    |      | 11.3.2 Difference between Unencrypted and Encrypted Bitstream |

|    |      | 11.3.3 Locating the AES Encryption                            |

|    | 11.4 | Side-Channel Key Extraction                                   |

|    |      | 11.4.1 Digital Pre-Processing                                 |

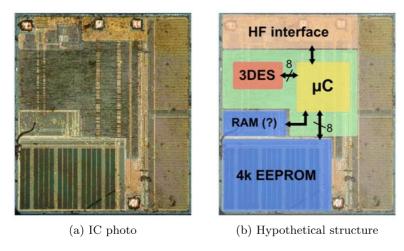

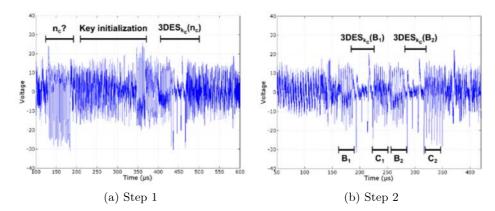

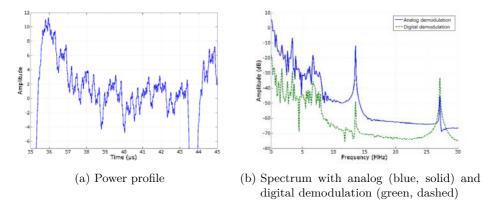

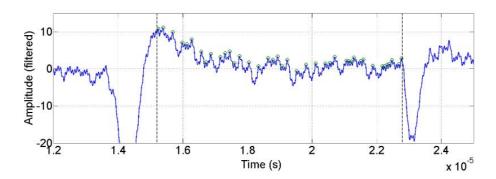

|    |      | 11.4.2 Hypothetical Architecture                              |

|    |      | 11.4.3 Results                                                |

|    |      |                                                               |

|     | 11.5               | Conclusion                                     | . 162 |  |  |  |  |

|-----|--------------------|------------------------------------------------|-------|--|--|--|--|

| IV  | Co                 | nclusion                                       | 163   |  |  |  |  |

| 12  | Atta               | acks and Countermeasures                       | 165   |  |  |  |  |

|     | 12.1               | Steps of a Real-World Attack                   | . 165 |  |  |  |  |

|     |                    | 12.1.1 Preparation                             | . 165 |  |  |  |  |

|     |                    | 12.1.2 Measurement                             | . 167 |  |  |  |  |

|     |                    | 12.1.3 Evaluation                              |       |  |  |  |  |

|     | 12.2               | Comparison of the Presented Attacks            | . 169 |  |  |  |  |

|     |                    | Reasons for Security Problems                  |       |  |  |  |  |

|     |                    | Responsible Disclosure                         |       |  |  |  |  |

|     | 12.5               | Countermeasures                                |       |  |  |  |  |

|     |                    | 12.5.1 Physical and Algorithmic Level          |       |  |  |  |  |

|     |                    | 12.5.2 Protocol Level                          |       |  |  |  |  |

|     |                    | 12.5.3 System Level                            | . 177 |  |  |  |  |

| 13  | Dire               | ctions for Future Research                     | 179   |  |  |  |  |

| _   |                    | Improving SCA Techniques                       |       |  |  |  |  |

|     |                    | 13.1.1 Measurement Methods                     |       |  |  |  |  |

|     |                    | 13.1.2 Processing of Side-Channel Traces       |       |  |  |  |  |

|     | 13.2               | Implementation Attacks and Reverse-Engineering |       |  |  |  |  |

|     |                    | 13.2.1 Attack Techniques                       | . 181 |  |  |  |  |

|     |                    | 13.2.2 Countermeasures                         | . 181 |  |  |  |  |

|     | 13.3               | Practical Implementation Attacks               | . 182 |  |  |  |  |

|     |                    | 13.3.1 Physical Layer of RF Devices            | . 182 |  |  |  |  |

|     |                    | 13.3.2 Contactless Smartcards and RFIDs        | . 183 |  |  |  |  |

|     |                    | 13.3.3 Access Control Systems                  | . 183 |  |  |  |  |

|     |                    | 13.3.4 FPGA Bitstream Encryption               | . 184 |  |  |  |  |

| V   | Ар                 | pendix                                         | 185   |  |  |  |  |

| Bil | oliogr             | raphy                                          | 187   |  |  |  |  |

| Lis | t of a             | Abbreviations                                  | 205   |  |  |  |  |

| Lis | List of Figures 2  |                                                |       |  |  |  |  |

| Lis | t of               | Tables                                         | 211   |  |  |  |  |

| Αb  | bout the Author 21 |                                                |       |  |  |  |  |

| Pu  | ublications 21     |                                                |       |  |  |  |  |

# Part I Preliminaries

## Chapter 1

## Introduction

In this chapter, the motivation for the research described in the thesis is established. Presenting numerous security-relevant applications of embedded devices, we introduce implementation attacks and show the need for a thorough analysis of real-world cryptographic devices with respect to this attack vector. Finally, we outline the structure of this thesis and summarize the main research contributions that are described in detail in the subsequent chapters.

#### Contents of this Chapter

| 1.1 | Motivation                        | 3 |

|-----|-----------------------------------|---|

| 1.2 | Implementation Attacks            | 6 |

| 1.3 | Structure of this Thesis          | 8 |

| 1.4 | Summary of Research Contributions | 9 |

#### 1.1 Motivation

Following the prevalent use of PCs in business and private applications, embedded computing devices have also become wide-spread in the past years. Numerous systems rely on Microcontrollers ( $\mu$ Cs), Field Programmable Gate Arrays (FPGAs), or Application Specific Integrated Circuits (ASICs). These computing devices are often invisible to the end-user. For example, a modern low-end car contains approximately 30 to 50 separate electronic units [iee09], controlling, amongst others, the engine, antilock brakes, the immobilizer, and the door locks. In contrast to a PC, an embedded system is usually not directly identifiable as such by a user and at the same time tends to be more safety or security-relevant:

For a car, an industrial machine, or an airplane, accidental malfunctions of the electronics or manipulations intentionally performed by an adversary can lead to severe material and monetary damage and in the worst case endanger human lives. In the context of electronic access control, e.g., wireless-controlled door locks, flaws in the underlying embedded system can enable an attacker to gain unauthorized access to a building, a threat especially relevant in the context of industrial espionage. Radio Frequency IDentification (RFID) transponders employed in contactless payment and ticketing systems may—if not sufficiently secured—be duplicated, incurring financial losses for the system operator [KSP10].

A different threat for RFIDs and Radio Frequency (RF) devices in general originates from the wireless nature of the interface. An adversary can both passively eavesdrop on legitimate communication or actively query an RFID transponder. Since the access to the wireless link cannot be easily restricted (as, e.g., for a cable medium), corresponding attacks can for instance affect the privacy of the users or allow an adversary to locate assets like freight containers in a supply chain RFID system.

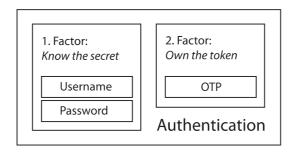

In the context of industrial espionage, attacks on embedded devices can be used to prepare the actual theft of confidential information. For example, corporate networks are today often secured with two-factor authentication, involving a hardware token in addition to the traditional username-password credentials. This rules out attacks that test passwords from a dictionary or perform an exhaustive search. However, as a consequence, the second authentication factor becomes subject to attacks itself. This was the case in the example of the attack on RSA's SecurID system [Bri11]. Although in this specific situation weaknesses of the backend network had been exploited, the attackers would certainly also have utilized flaws of the hardware token if they would have found any.

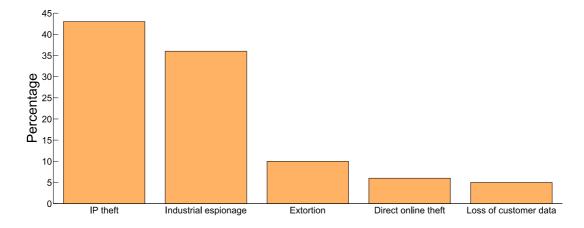

A 2011 study [Det11] regarding the costs due to cyber crime in the UK confirms the severity of this problem: While the cost to private users and governmental institutions is estimated to be £ 3.1 billion and £ 2.2 billion per year, respectively, [Det11] puts the figure for UK businesses at £ 21 billion per year. Although the magnitude of these numbers was questioned, e.g., in [Bre11], the report certainly allows to draw qualitative conclusions. In particular, it is interesting to examine which kind of attacks lead to the cost of £ 21 billion. Figure 1.1 summarizes the results of [Det11] in this respect, with Intellectual Property (IP) theft and industrial espionage accounting for approximately 79% of the overall financial damage. Surprisingly, more "obvious" attacks like extortion, direct online theft, and the loss of customer data are less dominant with a share of only 21%.

Figure 1.1: Distribution of costs for UK businesses due to cyber crime according to [Det11]

Note that IP theft ranks highest in Fig. 1.1 with over 40% of the total cost. Although IP theft is today mostly performed via the Internet, the high cost underlines the general relevance of the problem. Thus, from the perspective of the manufacturer of an (electronic) product, security may also mean that the product cannot be counterfeit by a competitor. This is the case both for low-end mass products like cellphone batteries or inkjet cartridges, but may also apply to expensive equipment like high-end network routers. Thus, corresponding devices either

use hardware components that inherently comprise protection mechanisms against counterfeit or contain additional special-purpose Integrated Circuits (ICs). In this case, an adversary might go to great lengths to overcome these countermeasures, since one-time access to the IP of one specific device allows to build duplicates of the respective product.

Certainly, there are numerous other kinds of applications that employ embedded systems with security-relevant functionality. However, in this thesis, we focus on case studies representing the mentioned examples, i.e., RFIDs, electronic locks, two-factor authentication tokens, anti-counterfeit ICs, and FPGAs.

As our targets or Devices Under Test (DUTs), we selected devices that are (i) in wide-spread use and (ii) were considered secure so far. Note that our research is not purely "destructive". Instead, we believe that an analysis of real-world products, eventually leading to successful attacks, is an important prerequisite for designing more secure embedded systems—which may, as outlined above, be used in cases where a failure can have severe consequences.

In a certain sense, the current state of the security of embedded devices can be compared to the situation for software when PCs became increasingly wide-spread. Until suitable attack techniques had been developed and been applied to real programs, most software (including operating systems) was highly susceptible to many kinds of malicious attacks. Only the cooperation between well-meaning "white hat hackers" and software developers helped to partially solve this problem—and even today, although many countermeasures are available, software is often still vulnerable due to its high complexity.

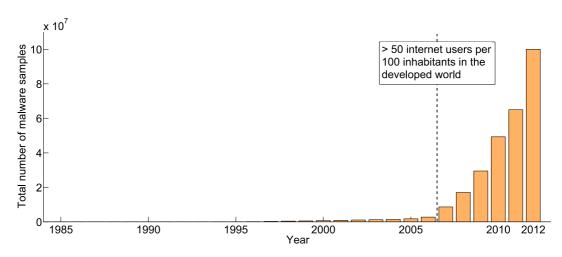

Figure 1.2: Total number of malware samples in the AV-Test database from 1984–2012 [AV-13]

In the case of attacks on software, a particular kind of organized crime has developed, focusing on exploiting flaws to, e.g., obtain login credentials and payment-related information or to create "botnets" used for illegal purposes. Two main reasons are in our eyes responsible for this situation: First, with most computers being connected via the Internet, newly discovered attacks can be easily carried out and quickly affect a huge number of PCs. As evident in Fig. 1.2, the number of PC malware samples in the AV-Test database [AV-13] began to strongly increase around 2006/2007. In these years, for the first time more than 50% of the inhabitants of developed countries had access to the Internet [Int11]. Second, until large-scale attacks started to appear on a regular basis, there was no obvious incentive for software manufacturers to

invest in security. Hence, the "investments" for criminal businesses to find and exploit flaws in wide-spread software packages were initially rather low.

To avoid a similar situation for embedded systems and to make sure that criminals are not the first ones to discover and exploit weaknesses, extensive research has to be carried out in this regard. To this end, in this thesis, we study several embedded systems and report the discovered security problems. Note that in most cases, the necessary equipment has a cost of less than USD 5,000, that is, the often hardware-based attacks could be performed at low cost without a complex and expensive lab setup.

Note that we aim at working with vendors to improve their products. Thus, as part of a responsible disclosure process, when we had found weaknesses, we informed the respective manufacturer several months before publishing our results. Depending on the concrete case and the resulting threat for practical applications, at times we left out certain details in our publications to prevent misuse of our findings. Also, we discussed suitable changes to a product with the vendor in order to help enhance the level of security.

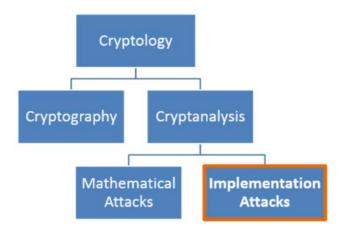

#### 1.2 Implementation Attacks

The field of cryptology can be subdivided into several areas. Following the classification of [PP10], cryptography deals with the design and implementation of cryptographic primitives, e.g., ciphers, hash functions, or signature schemes, and protocols which use these building blocks, e.g., for achieving confidentiality, integrity, or authentication. On the other hand, cryptanalysis attempts to find flaws in cryptographic constructions in order to estimate the actual security level of a scheme. In a continuous process, cryptanalysts analyze and potentially break cryptographic algorithms to allow designers to build systems not susceptible to the previously discovered attacks. In the long term, this led to the development of thoroughly analyzed and presumably highly secure algorithms like the AES.

Figure 1.3: Areas of cryptology according to [PP10]

*Implementation attacks* form a special class of cryptanalytical techniques. Traditional, mathematical analysis treats a cryptographic algorithm as an ideal, atomic operation, i.e., all com-

putations are performed correctly and internal states are never available to an adversary. While this assumption may (up to a certain degree) hold for PCs exchanging messages over a network, it is violated when an adversary has physical access to the actual implementation of cryptography, e.g., on a  $\mu$ C, FPGA, or ASIC.

In this case, several new ways for attacking the implementation rather than the underlying mathematical theory open up. For example, an adversary may disturb the computations on a device and subsequently evaluate the "faulty" results. This method termed Fault Injection (FI) was first described in [BDL97] and has since then been adapted to most cryptographic algorithms, including otherwise secure primitives like AES, 3DES, RSA, and Elliptic Curve Cryptography (ECC).

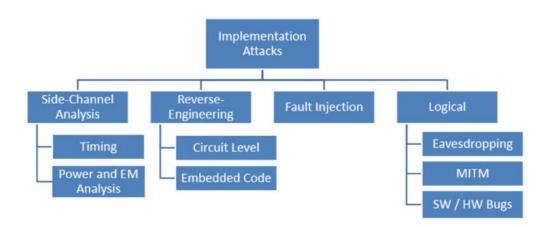

Shortly after the discovery of FI, Kocher et al. proposed Side-Channel Analysis (SCA) in 1999 [KJJ99]. In contrast to the active manipulation of a device required for FI, SCA is based on the passive observation of the target device, e.g., measuring the power consumption or Electro-Magnetic (EM) emanation while the cryptographic algorithm is executed. Using statistical methods, secret information, e.g., a cryptographic key, can be extracted in this way, often without tampering with the device. An overview over these and additional implementation attacks is given in Fig. 1.4.

Figure 1.4: Types of implementation and implementation-related attacks

Reverse-engineering can be seen as an implementation-related attack in the context of embedded systems: given access to embedded program code or an implementation in silicon on an IC, an adversary attempts to reconstruct for instance confidential, vendor-specific algorithms. In certain cases, reverse-engineering can serve as a preparatory step for side-channel attacks or FI to simplify the profiling of a DUT or to be able to communicate with the device at all (in the case of proprietary protocols). Logical attacks focus on flaws on the level of transmission and communication protocols. For example, an adversary may eavesdrop on unprotected data exchanges or act as a Man-In-The-Middle (MITM) between legitimate communication partners. Finally, embedded software and hardware implementations can, like every complex system, contain bugs that allow an attacker to compromise the security by, e.g., sending unexpected input data to a DUT.

Implementation attacks are techniques that initially originated from the practical analysis of real devices. For example, at the time of the discovery of SCA, high-security smartcards were allegedly susceptible to this attack vector. However, since vendors reacted relatively quickly and included countermeasures to prevent straightforward implementation attacks, the focus of the respective research area shifted to a more theoretical perspective, e.g., studying the statistical aspects of SCA.

Until 2008, there were no further reports of SCA being successfully applied on a large scale in the real world. The break of the wide-spread KeeLoq Remote Keyless Entry (RKE) scheme [EKM<sup>+</sup>08] using a side-channel attack changed this situation. Since SCA could in this case be used to extract a master key that allowed an adversary to compromise all products of a specific vendor, the practical threat due to implementation attacks became evident. In this thesis, we continue the analysis of real-world products, applying state-of-the-art SCA and, in addition, occasionally also related techniques like FI or reverse-engineering. Taking representative examples for different kinds of embedded systems as outlined in Sect. 1.1, we demonstrate the potential consequences of insufficient protection against implementation attacks.

#### 1.3 Structure of this Thesis

The steps performed for achieving the goal of this thesis can be summarized as follows:

- **Fundamentals** In Chap. 2, we recapitulate the current state-of-the-art for SCA, focusing on methods that are generally applicable. In the context of pre-processing of side-channel measurements, we develop a technique to partially automate the choice of respective parameters.

- **Tools** As a prerequisite for the practical application of implementation attacks, suitable tools for the communication with target devices, the acquisition and filtering of side-channel measurements, and for FI are necessary. In Chap. 3–5, we introduce the low-cost equipment utilized for this purpose.

- **Application** Using the described SCA methods and the developed tools, we analyze several real-world devices and demonstrate the numerous security problems we came across. The selected target devices are examples for the following embedded systems:

- (1) RFID transponders (Chap. 6 and Chap 7),

- (2) Electronic locking systems (Chap. 8),

- (3) Two-factor authentication tokens (Chap. 9),

- (4) Anti-counterfeit ICs (Chap. 10), and

- (5) FPGAs (Chap. 11).

- **Countermeasures** Examining the results of the practical analyses from a more general perspective, we identify reasons for the discovered security problems in Chap. 12. On this basis, suitable countermeasures on different levels are described.

- **Future Work** To conclude this thesis, in Chap. 13 directions for further research are outlined, both from the "destructive" perspective of the cryptanalyst and the constructive designer's point of view.

In the following Sect. 1.4, we give further details on the respective research contributions and the publications that form the basis for the results reported in this thesis.

#### 1.4 Summary of Research Contributions

As mentioned, the research described in this thesis was conducted in several related areas. The contributions include improved processing techniques for SCA and the development of a cost-effective toolchain for implementation attacks. As the main result, several DUTs are analyzed with respect to the susceptibility towards implementation attacks.

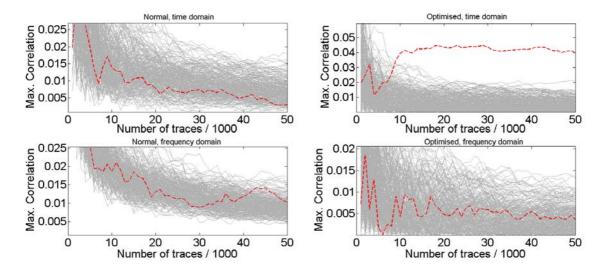

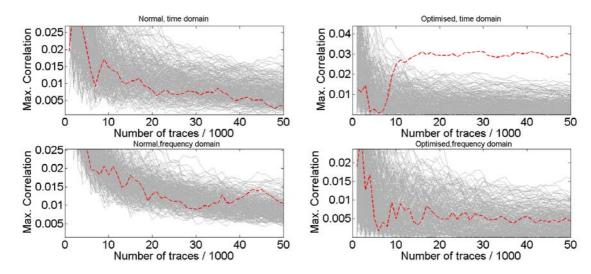

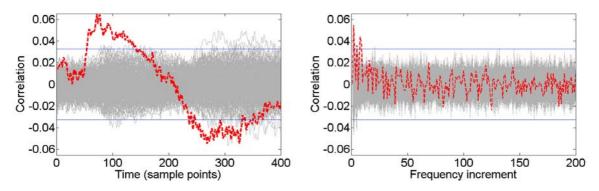

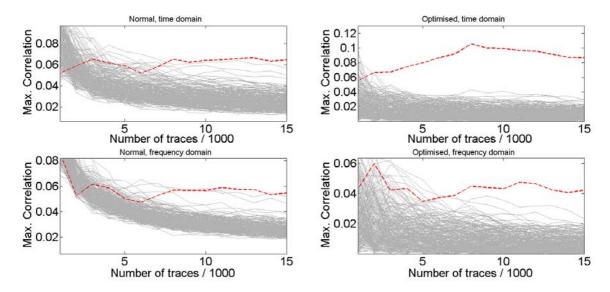

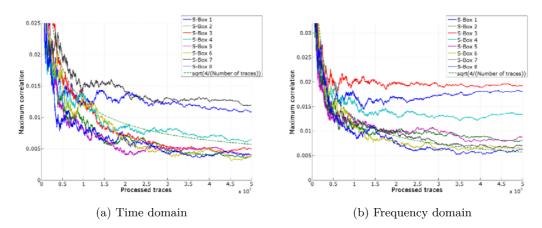

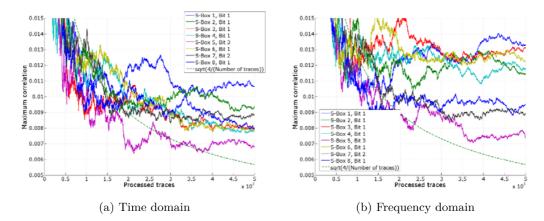

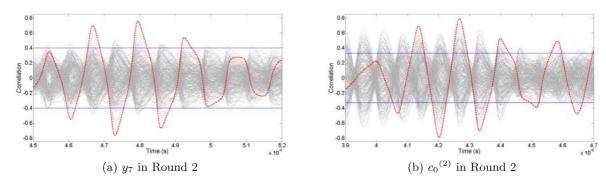

#### 1.4.1 SCA Pre-Processing

In the context of SCA, the measured side-channel signals are often subject to pre-processing before carrying out the actual attack. The parameters for the pre-processing, e.g., the cutoff frequency of a digital filter, are as of today mostly chosen manually. In Sect. 2.5, a method for the more systematic derivation of parameters for linear filters is described. Note that the proposed approach was developed following the practical attacks of Chap. 7–11, for which we often determined suitable pre-processing steps by exhaustively testing many parameter choices. The research in this section was published in [OP13].

#### 1.4.2 Tools

The toolchain used for this thesis comprises numerous modules due to the manifold tasks one faces when analyzing real products. Apart from software components for data acquisition, processing, and statistical evaluation, oscilloscopes and an FPGA-based setup for implementation attacks were utilized. Custom analog filters were developed to increase the success rate of SCA of contactless RFID smartcards.

#### Measurement and Evaluation

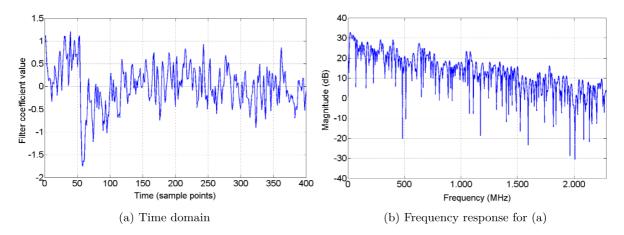

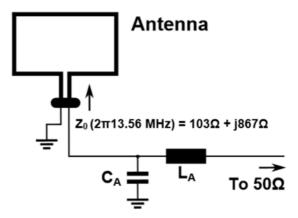

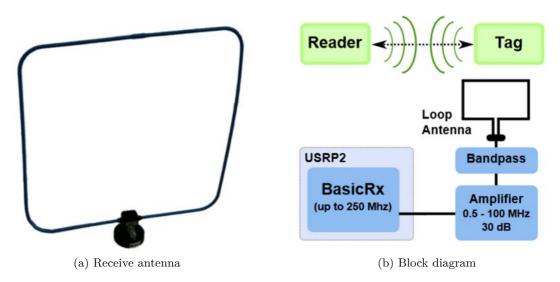

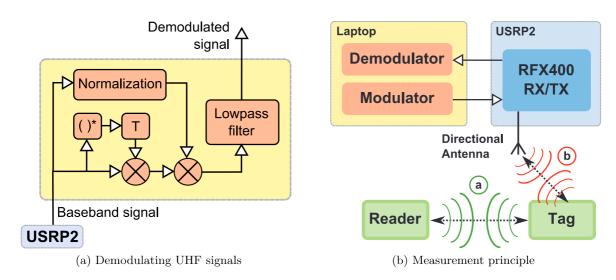

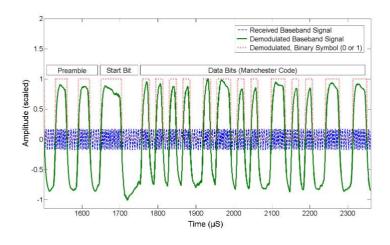

For acquiring side-channel signals, two Digital Storage Oscilloscopes (DSOs) were employed to digitize measurements of the power consumption and the EM emanation of a DUT, cf. Sect. 3.2. For controlling the measurement process and for evaluating the obtained waveforms, a flexible framework for according software applications was developed, cf. Sect. 3.2.3 and Sect. 3.3. In addition to tools specifically designed for side-channel attacks, we also employed Software-Defined Radio (SDR) devices for receiving and transmitting RF signals as described in Sect. 3.1. The SDRs were, amongst others, utilized for determining the actual ranges of RFIDs in Chap. 6.

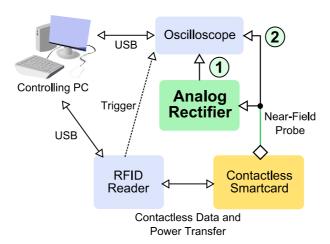

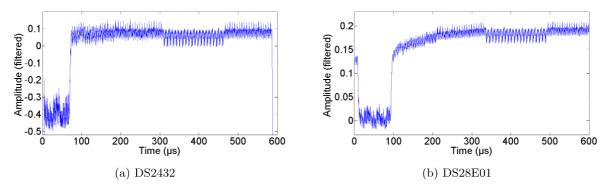

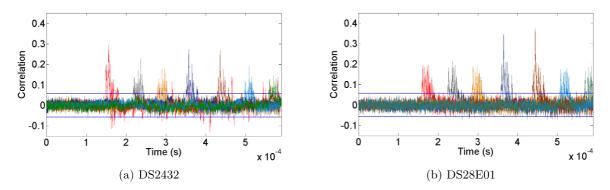

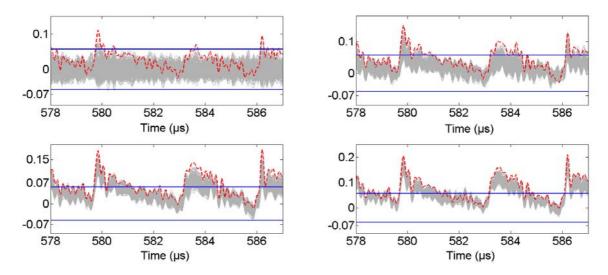

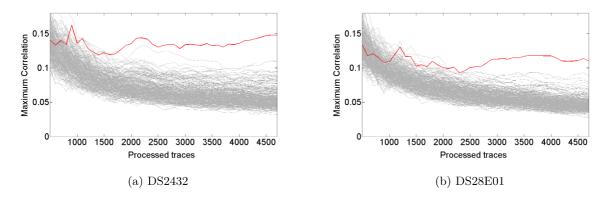

#### Pre-Processing for SCA of RFID

When performing SCA of contactless smartcards, the presence of a strong reader signal complicates the direct measurement of the side-channel leakage of the DUT. Special analog circuits are beneficial to isolate and amplify the relevant signal before converting it into digital data with a DSO. In Chap. 4, such components based on incoherent demodulation are introduced. The developed demodulator is subsequently applied for the analysis of the Mifare DESFire MF3ICD40 smartcard in Chap. 7. The research in this section was published in [KOP12].

#### GIAnT: A Platform for Implementation Attacks

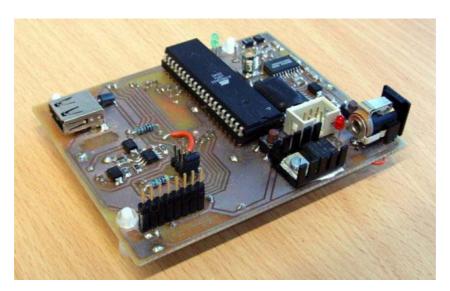

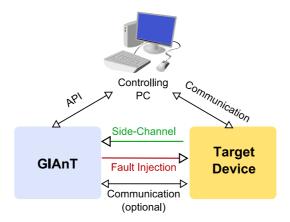

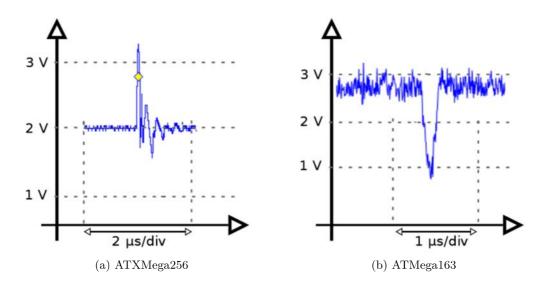

Since commercial solutions for conducting implementation attacks are usually expensive, we created the custom, open-source platform GIAnT presented in Chap. 5. The device can for instance be employed to inject faults by means of supply voltage manipulations, to digitize analog signals, and to communicate with a wide variety of potential DUTs. Verifying the effectiveness of our platform, we show that cryptographic implementations on (unprotected) Atmel ATMega and ATXMega  $\mu$ Cs can be attacked by means of voltage manipulations. Although the specifications of the GIAnT cannot compete with those of expensive high-end equipment, the provided functionality was sufficient for the purposes of this thesis. Moreover, because the GIAnT can be built for approximately USD 300, basic techniques for implementation attacks are made accessible to a wide audience, e.g., allowing designers to directly test their products. This contribution is an improved version of the author's research published in [KOP10].

#### 1.4.3 Practical Implementation Attacks

Applying the developed toolchain, we analyze embedded cryptographic devices with respect to implementation attacks and SCA in particular. Doing so, we found weaknesses in several wide-spread commercial products, allowing to extract secrets like cryptographic keys within a few minutes to a few hours. Note that in the case of a successful attack, the affected vendor was informed several months ahead of time before the publication. We discussed suitable countermeasures and provided a summary of our results to allow the manufacturer to inform the customers before our discovery was made public.

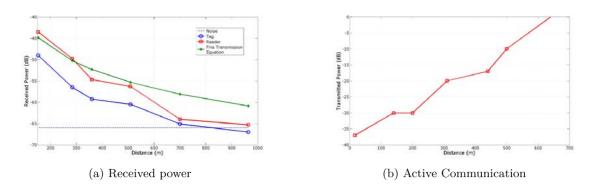

#### **RFID Range Measurements**

As an introductory example, we demonstrate the problems that arise when protocols lacking cryptographic protection are executed over wireless links in Chap. 6. More precisely, we show that the effective range for active RFIDs operating at 433.92 MHz clearly exceed the specified maximum distance. To compare the results to 13.56 MHz RFIDs as, e.g., used for contactless smartcards or Near Field Communication (NFC) cellphones, we conducted a similar study for according devices as well. The security problems resulting from our findings, including the unnoticed detection, duplication, and manipulation of transponders from a distance, demonstrate the need for suitable cryptographic protection to prevent such implementation attacks targeting the physical layer of the wireless interface. The research in this section was published in [KOP11a].

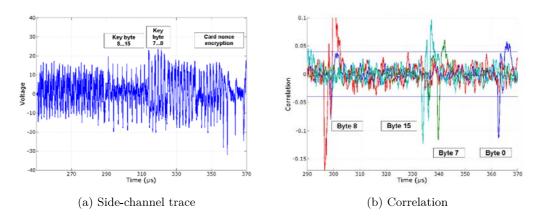

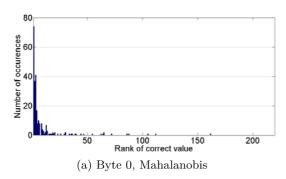

#### Mifare DESFire MF3ICD40

In order to illustrate that a smartcard implementing analytically secure algorithms like 3DES can still be susceptible to SCA, we focus on the Mifare DESFire MF3ICD40 in Chap. 7. This RFID, the secure variant of the broken Mifare Classic card, is used in several real-world installations, including large-scale public transport systems. Employing various state-of-the art methods and special filter circuits, we present full key-extraction attacks on this device, circumventing countermeasures against SCA. Applying the developed techniques for a case study of a real public transport system, we gain insight into the design of a practical application

and identify potential security issues in this regard. The research in this section was published in [OP11, KOP11b].

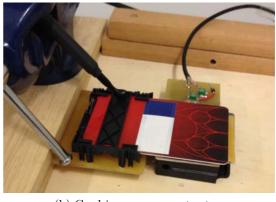

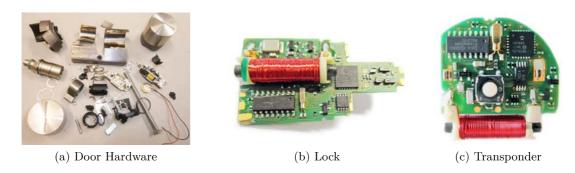

#### SimonsVoss Access Control System

According to our observations, proprietary cryptographic algorithms and protocols are still prevalent in modern electronic locking systems, which are used to control the access to both private and in particular corporate buildings. In Chap. 8, the SimonsVoss system 3060 "G2" is examined, applying reverse-engineering methods to recover the used undisclosed algorithms. Note that the vendor ignored SCA during the development and solely relied on obscurity-based countermeasures. Hence, a side-channel attack on the electronics of a lock can be used to extract a master key, compromising the security of an entire installation. The research in this section was published in  $[OSS^+13, SDK^+13]$ .

#### The Yubikey One-Time Password Token

Two-factor authentication is becoming increasingly popular to solve the problems of traditional username-password credentials. We show that network operators using hardware tokens for this purpose have to take implementation attacks like SCA into account, a threat formerly irrelevant in the context of user authentication. To this end, we present a non-invasive side-channel attack on the Yubikey 2, a widely used USB token for generating one-time passwords. The research in this section will be published in [ORP13].

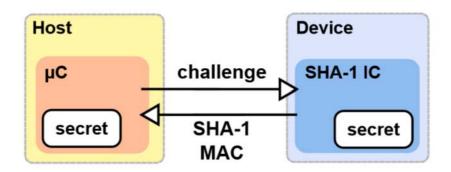

#### Maxim SHA-1 Product Authentication ICs

Hardware solutions are employed not only for authenticating users: ICs ensuring the genuineness of commercial devices, ranging from mass products to high-end equipment, are used to counter product piracy. Obviously, such components need to apply sound cryptographic algorithms to rule out "trivial" and analytical attacks. Yet, the threat due to SCA is given less attention. Analyzing two SHA-1-based ICs by Maxim Integrated, we found FI and SCA weaknesses, allowing to extract the full secret and subsequently "clone" the devices.

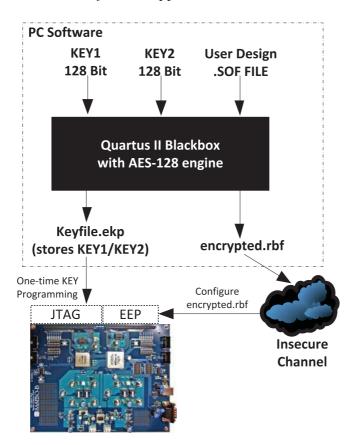

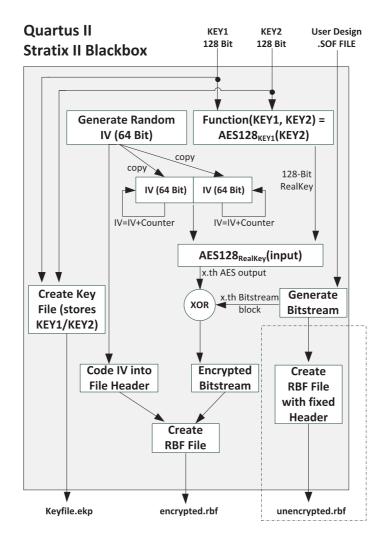

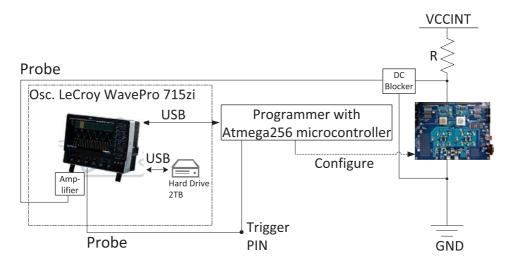

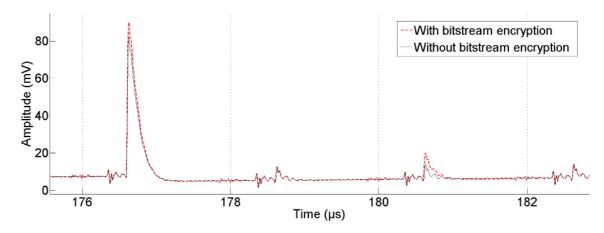

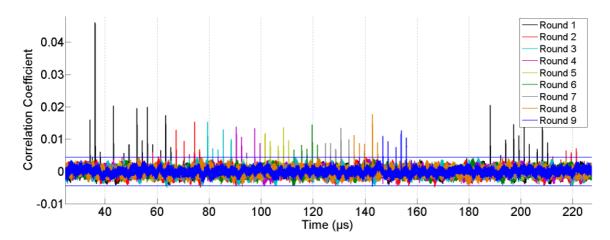

#### Altera FPGA Bitstream Encryption

In the context of product counterfeit, FPGA-based products face a special problem. Since the configuration bitstream of the FPGA usually resides in external memory, an adversary has direct access to a vendor's IP. To solve this problem, FPGAs comprise functionality to encrypt the configuration data. Nevertheless, these functions have been shown to be unprotected against implementation attacks for several FPGA families made by Xilinx and Actel. In Chap. 11, we demonstrate that the same problem exists for the third major FPGA vendor Altera. Having reverse-engineered the proprietary (AES-based) encryption scheme from the PC software Quartus II, successful key extraction attacks on Altera Stratix II FPGAs can be realized, allowing an adversary to clone, decrypt, and manipulate the FPGA's bitstream. The research in this section was published in [MOPS13].

## Chapter 2

## **Side-Channel Analysis**

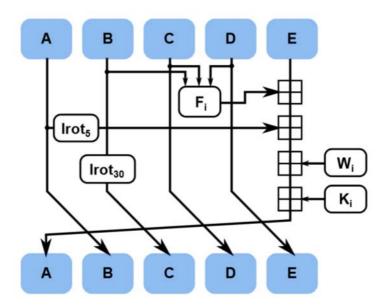

Following the initial discovery of Simple Power Analysis and Differential Power Analysis in 1999, a significant number of improved techniques for SCA has been proposed. In this chapter, we give an overview over the most important results, describing possible sources of side-channel leakage and the most common evaluation methods to recover cryptographic secrets by means of SCA. We then focus on preprocessing techniques that have been shown to significantly improve the success rate of side-channel attacks. To this end, we propose a method to automatically derive (in a certain sense) optimal parameters for linear filters applied to SCA measurements.

#### Contents of this Chapter

| 2.1        | Introduction                              | 13         |

|------------|-------------------------------------------|------------|

| 2.2        | Physical Side Channels                    | 14         |

| 2.3        | Evaluation Methods                        | <b>2</b> 0 |

| 2.4        | Pre-Processing Methods                    | <b>26</b>  |

| <b>2.5</b> | Finding Optimal Linear Transforms for SCA | <b>2</b> 8 |

| 2.6        | Conclusion                                | 38         |

#### 2.1 Introduction

As introduced in Sect. 1.2, SCA can be used to extract cryptographic secrets irregardless of the cryptanalytical security of an algorithm by obtaining additional information on, e.g., an intermediate state via a physical side-channel.

The success of a side-channel attack depends on two main parts. First, the channel of the physical leakage has to be identified and captured in an adequate manner. To this end, Sect. 2.2 describes various well-known side-channels.

Second, suitable evaluation methods to reconstruct the targeted secret from the acquired measurements are needed. In Sect. 2.3, we focus on the—in practice still most common—techniques Simple Power Analysis (SPA), Differential Power Analysis (DPA), Correlation Power Analysis (CPA), and Template Attacks (TAs).

Often, the evaluation methods benefit (i.e., less measurements are needed to recover the secret) from additional (digital) pre-processing of the measurements. In Sect. 2.4, we accordingly summarize the use of Digital Signal Processing (DSP) techniques in the context of SCA. Subsequently, in Sect. 2.5, we detail on utilizing numerical optimization algorithms in order

to determine (in a certain sense) optimal parameters for linear pre-processing. This chapter is concluded in Sect. 2.6 with a summary of the main results.

#### 2.2 Physical Side Channels

The actual physical side-channel leaking information on, e.g., a cryptographic secret, can take various forms. In this section, we give an overview over the physical side channels most often utilized in the literature, i.e., the timing (Sect. 2.2.1), the power consumption (Sect. 2.2.2), and the EM emanation (Sect. 2.2.3) of a DUT during the execution of a cryptographic algorithm. Additionally, in Sect. 2.2.4, we briefly describe more "exotic" leakage sources like the photonic emission of a semiconductor circuit.

#### 2.2.1 Execution Time

In straightforward implementations of cryptographic algorithms, conditional statements can cause a dependency of the overall execution time on the processed data, possibly including the secret. For example, the basic Square-and-Multiply (SAM) algorithm given in Alg. 1 carries out an additional multiplication if a specific bit in the exponent is set. If Alg. 1 is used to sign a message with RSA, the runtime of the algorithm would thus partially be determined by the secret exponent d.

```

Algorithm 1 The left-to-right SAM algorithm for an RSA signature

```

```

Require: Basis x

Require: Modulus n

Require: w-bit exponent d

Ensure: y = x^d \mod n

y \leftarrow 1

for i = w - 1 to 0 do

// Always square

y \leftarrow y^2 \mod n

// Exponent-dependent multiplication

if bit i of d is set then

y \leftarrow y \cdot x \mod n

end if

end for

return y

```

In [Koc96], Kocher proposed an attack on the SAM algorithm with the additional requirement that the execution time of a single multiplication, e.g.,  $y \leftarrow y \cdot x \mod n$ , varies depending on the operands x and y. Then, by predicting the runtime for the cases "bit w-1 of d set" and "bit w-1 of d not set" for varying inputs and comparing the prediction to measured runtimes (using the variance), bit w-1 of d can be recovered. This process is then repeated for each subsequent bit—taking the previously recovered bits into account—until the exponent has been completely determined.

A multitude of different timing attacks has been described in the literature following the initial discovery. A relatively recent example are cache-timing attacks [Ber]. These attacks are based on the fact that modern CPUs contain (multiple) fast caches. Accessing a specific value, e.g., from a Look-Up Table (LUT), for the first time is thus slower than subsequent accesses. The first time, the value is loaded from the slower Random Access Memory (RAM) (and stored in the cache), after that, it resides in the cache and can hence be retrieved faster.

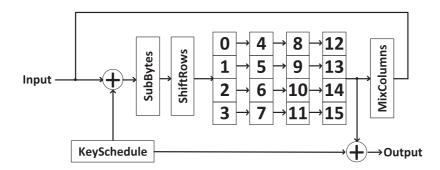

When an S-box, e.g., of the AES, is implemented using a LUT, this introduces a key-dependent timing because the input to the S-box is the XOR of a plaintext and key byte (for the example of the AES). Thus, predicting the timing for all 256 candidates for a key byte and statistically comparing the prediction to the actual measurements allows to recover the full AES key. This attack was found to be applicable to the quasi-standard library OpenSSL—even over a network connection—in [Ber].

In this thesis, we did not directly focus on timing attacks, however, we observed two real-world examples of cryptographic algorithms with non-constant execution time for the DESFire MF3ICD40 (Chap. 7) and the Yubikey 2 (Chap. 9). Nevertheless, in both cases, we were unable to perform a timing attack. For other DUTs, e.g., Altera Stratix II FPGAs (Chap. 11) or Maxim SHA-1 ICs (Chap. 10), a hardware implementation of the employed algorithms lead to a constant, data-independent timing behavior.

#### 2.2.2 Power Consumption

For an electronic circuit, the consumed power is not constant but depends on the processed data. For example, switching the input and thus the output of a Complementary Metal Oxide Semiconductor (CMOS) inverter leads to an increased current being drawn until the switching is "completed". Dynamic Random Access Memory (DRAM) memory stores information as the state of a capacitor (charged, not charged) and requires current for storing (and keeping) the "charged" state.

Thus, using the current consumption as a side channel to extract a secret from a cryptographic circuit seems to be a somewhat natural approach, and the first publications on SCA [KJJ99] were based on this leakage source. In the simplest case, the state of a key bit (set or not set) can be directly "read off" a current consumption measurement, otherwise, more complicated techniques are necessary, cf. Sect. 2.3.

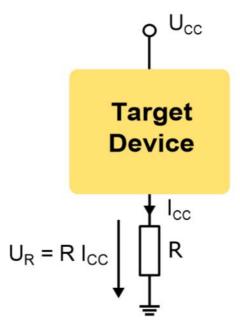

A typical measurement setup for measuring the current consumption is depicted in Fig. 2.1. A (preferably small) resistor R is inserted into the ground line of the DUT and the voltage drop over the resistor is measured using a DSO or a similar digitizer. The resulting time and value-discrete current consumption waveform is usually referred to as *power trace* or simply trace in the literature.

Note that in the SCA research area, it is common to use the term "power", e.g., as in "power analysis" or "power trace", although technically the current consumption is measured in Fig. 2.1: The measured voltage  $U_R = R \cdot I_{\rm CC}$  is proportional to the consumed current  $I_{\rm CC}$ , while the power consumption of the DUT is

$$P_{\text{DUT}} = I_{\text{CC}} \cdot (U_{\text{CC}} - U_R) = U_{\text{CC}} \cdot I_{\text{CC}} - R \cdot I_{\text{CC}}^2$$

which contains an additional term proportional to the squared current  $I_{\text{CC}}^2$  due to the resistor affecting the circuit. For an ideal current measurement, i.e., R=0, the term with  $I_{\text{CC}}^2$

Figure 2.1: Typical setup for measurement of current consumption traces: a shunt resistor is inserted into the ground path

would vanish, and the measured current  $I_{\rm CC}$  would indeed be exactly proportional to the power consumption  $P_{\rm DUT} = I_{\rm CC} \cdot U_{\rm CC}$  for a constant supply voltage  $U_{\rm CC}$ .

However, following the common practice, we occasionally use the term "power trace" or "measurement of the power consumption" also for the case R>0 in this thesis, whereas a more correct expression would use "current". The term "power" can be understood as referring to a measurement involving the power supply lines of a circuit.

In general, in this thesis, we assume that the current consumption of a DUT at a point in time t has the form of Eqn. 2.1:

$$i(t) = I_{const} + i_{dyn}(t)$$

(2.1)

where  $I_{const}$  is the static part and  $i_{dyn}(t)$  the fraction caused by internal operations, e.g., amongst others, intermediate values being manipulated during a cryptographic operation. Additionally, in reality, a noise term is added to Eqn. 2.1, caused both by measurement noise and algorithmic noise (e.g., interrupts, time desynchronization, and so on). This yields Eqn. 2.2:

$$i_{noisy}(t) = I_{const} + i_{dyn}(t) + \mathcal{N}\left(\mu_{noise}, \sigma_{noise}^2\right)$$

(2.2)

where  $\mathcal{N}\left(\mu_{noise}, \sigma_{noise}^2\right)$  is a normally distributed random variable with mean  $\mu_{noise}$  and variance  $\sigma_{noise}^2$ .

The measurement of the current consumption has several disadvantages. First, it requires a modification of the circuit to insert the measurement resistor, except for devices with exposed ground and  $U_{\rm CC}$  contacts like smartcards or simple USB tokens. For complex circuits, many ground lines may have to be cut, for example, to acquire traces for a  $\mu$ C. Second, blocking

and smoothing capacitors often have to be removed, a fact that makes an attack detectable afterwards.

For example, in the case of the SimonsVoss door lock Printed Circuit Board (PCB) (cf. Chap. 8), a large electrolyte capacitor led to heavily lowpass-filtered traces, rendering an attack based on the power consumption of the actually extremely SCA-vulnerable  $\mu$ C impossible. Finally, even worse, ICs might have on-chip voltage regulators that cause a similar smoothing and cannot be removed at all. This was for instance likely the case for the Yubikey 2 USB token, cf. Chap. 9.

#### 2.2.3 Electro-Magnetic Emanation

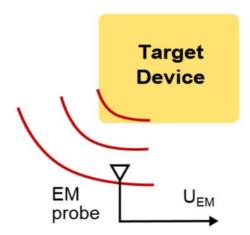

In contrast to power measurements (Sect. 2.2.2), attacks based on the EM emanation [AARR03] usually require no modifications of the DUT or the surrounding circuitry of an IC. Figure 2.2 shows the typical measurement setup for EM analysis. A suitable EM probe is placed close to the DUT, whereas the exact position depends on the concrete attack scenario.

Figure 2.2: Typical setup for measurement of EM traces: an EM probe is placed close to the DUT

Depending of the type of the probe, either the electrical field E or the magnetic field H is primarily acquired. In addition, the exact nature of the leakage depends on the location of the probe. We describe the general cases of the probe close to the power supply pins and directly on the chip surface in Sect. 2.2.3 and Sect. 2.2.3, respectively. Besides, we focus on the special case of RFIDs—as a prerequisite of the analysis of the Mifare DESFire MF3ICD40 in Chap. 7—and outline methods to recover the side-channel signal in the presence of an RFID reader field.

#### **Power Supply Pins**

In many EM-based SCA attacks, relatively large magnetic probes are employed. For example, the probes used in this thesis (cf. Sect. 3.2.2) have a spatial resolution of a few millimeters, which is in the same range as the length of one side of a usual silicon die. In a Bachelor's thesis co-supervised by the author of the present thesis [Sch10], EM measurements with similar probes were compared to power traces. As a result, it turned out that such EM traces mainly

correspond to a wireless measurement of the DUT's current consumption. Accordingly, the best results were obtained for the EM probe placed on top of the supply voltage or ground pins of the DUT.

However, EM measurements have, apart from not requiring modifications of the DUT, the advantage that they can isolate the leakage of one specific IC on a larger PCB. As mentioned in Sect. 2.2.2, the power traces acquired for the SimonsVoss door lock analyzed in Chap. 8 were flattened by a capacitor and contained additional distortion from an ASIC not performing cryptographic operations. To isolate the side-channel leakage of the relevant  $\mu$ C, an EM probe on top of one of the ground pins of the  $\mu$ C yielded a signal suitable for SCA.

#### **Chip Surface**

In [Sch10], the wireless measurement of the power consumption was compared to traces acquired with an EM probe directly on the surface of the chip. To this end, the analyzed DUTs were decapsulated with fuming nitric acid to expose the silicon die. As a result, no location-dependent leakage could be identified, and side-channel attacks usually required a higher number of trace to succeed compared to direct and EM measurements of the supply lines.

A reason for this result may have been the insufficient spatial resolution of the employed probes. In [HMH<sup>+</sup>13], Heyszl et al. show that with high-resolution probes (approximately 100 µm resolution), the EM leakage of specific functional parts of an FPGA can be localized. These EM measurements lead to a significantly higher Signal to Noise Ratio (SNR) and thus reduce the number of required traces for SCA. As a side note, the authors of [HMH<sup>+</sup>13] mention that the leakage results from the magnetic component of the EM field, a statement that coincides with the findings in [Sch10].

#### **RFID** and **Contactless Smartcards**

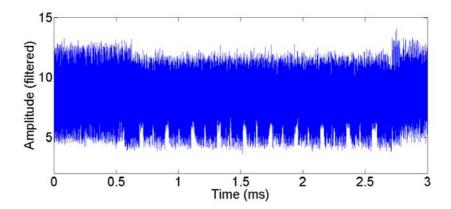

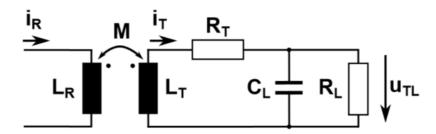

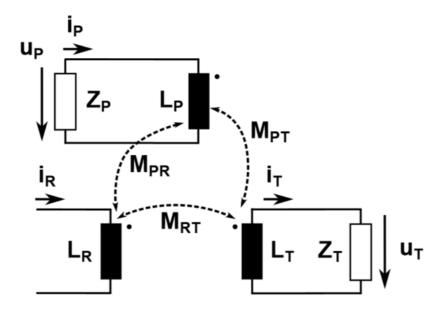

For RFIDs, the energy for operation is supplied wirelessly using magnetic coupling. As proposed in [KOP09, KOP12], this gives rise to a different leakage mechanism compared to contact-based devices. In a similar manner as for regular data transmission, the 13.56 MHz field generated by the reader is load-modulated by the power consumption of an RFID, also cf. Chap. 6.3.1 for further details. However, for data transmission, the fluctuations of the EM field are intentional and far stronger in magnitude.

Thus, in an RFID setting, the amplitude of the reader signal is modulated by i(t) (given in Eqn. 2.1), resulting in Eqn. 2.3 (neglecting the noise term of Eqn. 2.2). Note that in the case of RFID, the dynamic portion of the power consumption is far weaker than the static part, i.e.,  $|i_{dyn}(t)| \ll I_{const}$ . The leakage exploitable for an SCA thus heavily depends on the quality of the isolation and amplification of  $i_{dyn}(t)$ .

$$s(t) = i(t) \cdot \cos(\omega_r \cdot t) = (I_{const} + i_{dym}(t)) \cdot \cos(\omega_r \cdot t)$$

(2.3)

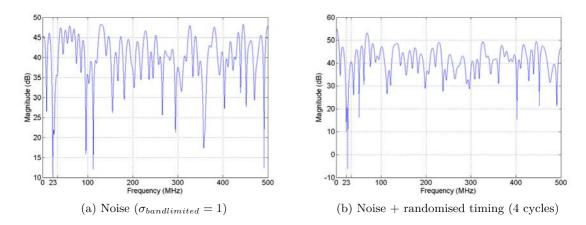

where  $\omega_r = 2\pi f_r$ ,  $f_r = 13.56$  MHz is the standard carrier frequency. Clearly, the extraction of i(t) (and especially of the weak dynamic portion) from s(t) can be done using amplitude demodulation, cf. for instance [SBS66]. In practice, "incoherent" techniques (i.e., for which a separate, unmodulated carrier signal is not necessary) based on rectification (often called envelope detection) are very common, and in this section, we follow that approach as well. The

principle due to which rectification can be used for demodulation is best understood in the frequency domain, following [Och06]. First note that, as stated above,  $|i_{dyn}(t)| \ll I_{const}$  and hence

$$|s(t)| = |I_{const} + i_{dyn}(t)| \cdot |\cos(\omega_r \cdot t)| = (I_{const} + i_{dyn}(t)) \cdot |\cos(\omega_r \cdot t)|$$

Let  $I(j\omega) = \text{DFT}\{i(t)\} = \text{DFT}\{I_{const} + i_{dyn}(t)\}$  denote the frequency domain representation of the signal that is to be reconstructed. By expanding  $|\cos(\omega_r \cdot t)|$  using its Fourier series, one obtains the spectrum of the rectified signal:

DFT {

$$|s(t)|$$

} = DFT { $i(t) \cdot |\cos(\omega_r \cdot t)|$ } = DFT { $i(t) \cdot \frac{2}{\pi} \sum_{\nu=-\infty}^{\infty} \frac{(-1)^{\nu}}{1-4\nu^2} e^{j2\nu\omega_r t}$ }

=  $\frac{2}{\pi} \sum_{\nu=-\infty}^{\infty} \frac{(-1)^{\nu}}{1-4\nu^2}$ DFT { $i(t) \cdot e^{j2\nu\omega_r t}$ } =  $\frac{2}{\pi} \sum_{\nu=-\infty}^{\infty} \frac{(-1)^{\nu}}{1-4\nu^2} I(j\omega - j2\nu\omega_r)$

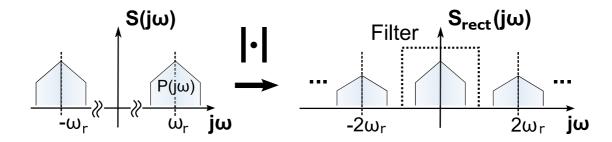

The rectified signal is essentially formed by the spectrum of  $I_{const} + i_{dyn}(t)$ , which, however, is (scaled and) repeated at all even multiples of the carrier frequency  $\omega_r = 2\pi$  13.56 MHz. Thus, the first repetition occurs at 27.12 MHz as depicted in Fig. 2.3. Using a lowpass filter with a cutoff frequency less than 13.56 MHz isolates the desired signal i(t). The constant term  $I_{const}$  can be removed with a highpass filter that only blocks the DC and very low-frequency components.

Figure 2.3: Full-wave rectification in the frequency domain

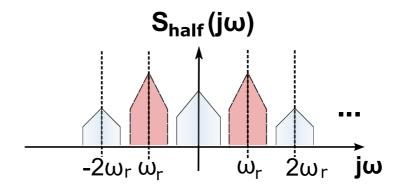

Note that in practice, often, the half-wave approach is used, discarding the negative part of s(t). This approach has the advantage that it can be realized with one diode, whereas full-wave rectification requires more complex circuitry. The remaining half-period of the sine-shaped signal can be mathematically expressed as  $\frac{1}{2}(s(t) + |s(t)|)$ . In terms of the achievable bandwidth for receiving the modulating signal i(t), full-wave rectification allows a maximum bandwidth of  $B_{\rm full} = 13.56\,{\rm MHz}$ , whereas the half-wave method limits it to  $B_{\rm half} = ^{13.56\,{\rm MHz}/2}$  This is due to the fact that the resulting spectrum is essentially the sum of the spectrum of the original and the rectified signal, i.e.

$$\mathrm{DFT}\left\{\frac{1}{2}\left(s\left(t\right)+\left|s\left(t\right)\right|\right)\right\} = \frac{1}{2}\left(\mathrm{DFT}\left\{s\left(t\right)\right\} + \mathrm{DFT}\left\{\left|s\left(t\right)\right|\right\}\right)$$

This results in a frequency-domain representation in which the first repetition occurs at  $\omega_r = 2\pi \ 13.56 \,\text{MHz}$  as depicted in Fig. 2.4. In comparison to Fig. 2.3, the spectral components due to the addition of the non-rectified signal s(t) (red, dashed in Fig. 2.4) require the lowpass

filter to have a cutoff frequency less than  $^{13.56\,\mathrm{MHz}/2}$  and hence lead to the mentioned reduction in bandwidth.

Figure 2.4: Half-wave rectification in the frequency domain. Red, dashed spectral components are due to the addition of the original signal

#### 2.2.4 Other Side Channels

Apart from the classical side channels power consumption, EM emanation, and timing, a variety of more "exotic" leakage sources has been reported in the literature. In [ST04], it was shown that the acoustic emissions of a standard PC, e.g., caused by high-frequency vibrations of capacitors on the mainboard, can be used to perform timing attacks and distinguish CPU operations. In a similar direction, in [BDG<sup>+</sup>10] acoustic recordings were employed to reconstruct the text printed with a dot-matrix printer.

For semiconductors, Photonic Emission Analysis (PEA) enables the observation of active ICs down to the gate level [FH08, SNK $^+$ 12]. By repeatedly taking photographs through a near-infrared microscope and averaging over hundreds of thousand runs, a complete map of the DUT's state at one point in time can be computed, with a resolution of approximately 1  $\mu$ m in [SNK $^+$ 12]. Besides, single-pixel detector can target a specific part of the DUT, e.g., an S-box output, to record the optical equivalent of a classical EM or power trace.

#### 2.3 Evaluation Methods